SPI: Serial Peripheral Interface

This article introduces the SPI (Serial Peripheral Interface) bus.

Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial communication interface specification used for short distance communication, primarily in embedded systems. The interface was developed by Motorola and has become a de facto standard. Typical applications include Secure Digital cards and liquid crystal displays.

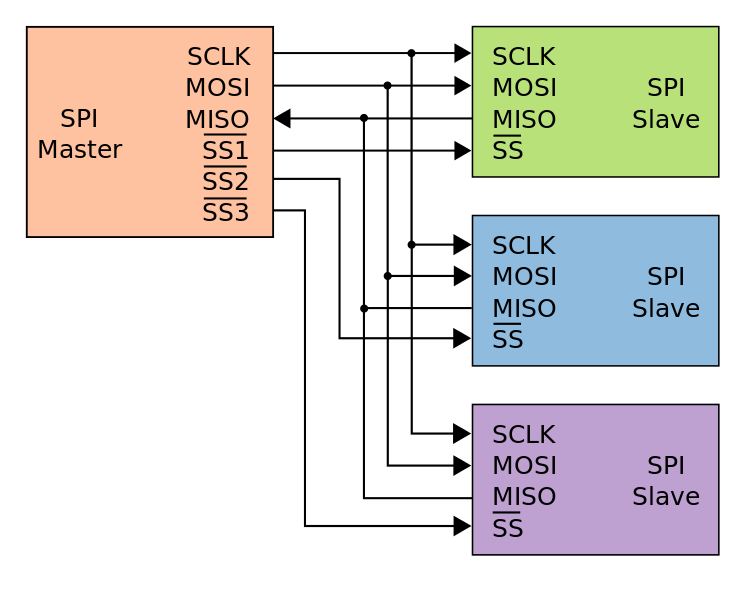

SPI devices communicate in full duplex mode using a master-slave architecture with a single master. The master device originates the frame for reading and writing. Multiple slave devices are supported through selection with individual slave select (SS) lines.

Sometimes SPI is called a four-wire serial bus, contrasting with three-, two-, and one-wire serial buses. The SPI may be accurately described as a synchronous serial interface, but it is different from the Synchronous Serial Interface (SSI) protocol, which is also a four-wire synchronous serial communication protocol, but employs differential signaling and provides only a single simplex communication channel.

Interface

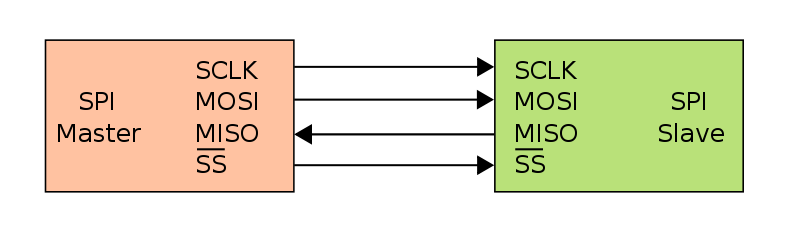

The SPI bus specifies four logic signals:

- SCLK: Serial Clock (output from master).

- MOSI: Master Output, Slave Input (output from master).

- MISO: Master Input, Slave Output (output from slave).

- SSEL: Slave Select (active low, output from master), also named SS.

Architecture

Typical SPI bus: single master to single slave

Typical SPI bus: single master to three independent slaves

NOTE: There are three SS ports on master, and each one of them conntects to one slave.

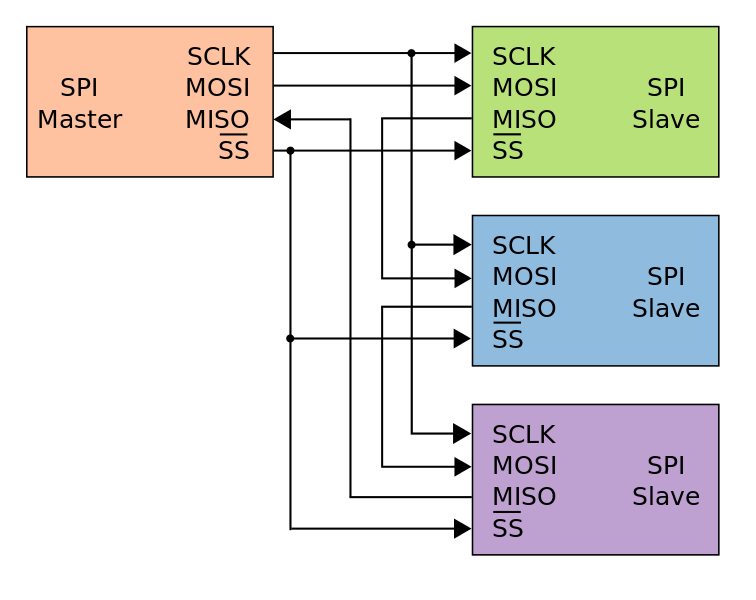

Daisy-chained SPI bus: master and cooperative slaves

NOTE: When cascading several SPI devices, they are treated as one slave and therefore connected to the same chip select.

Two-wire / Three-wire SPI

某些情况下,也可以用 3 根线的 SPI 或者 2 根线的 SPI 进行通信。例如,主机只给从机发送命令,从机不需要回复数据时,那么 MISO 就可以不要;而在主机只读取从机的数据,不需要给从机发送指令时,那 MOSI 就可以不要;当一个主机一个从机的时候,从机的片选有时可以固定为有效电平而一直处于使能状态,那么 SSEL 就可以不要;此时如果再加上主机只给从机发送数据,那么 SSEL 和 MISO 都可以不要;如果主机只读取从机送来的数据,SSEL 和 MOSI 都可以不要。

Operation

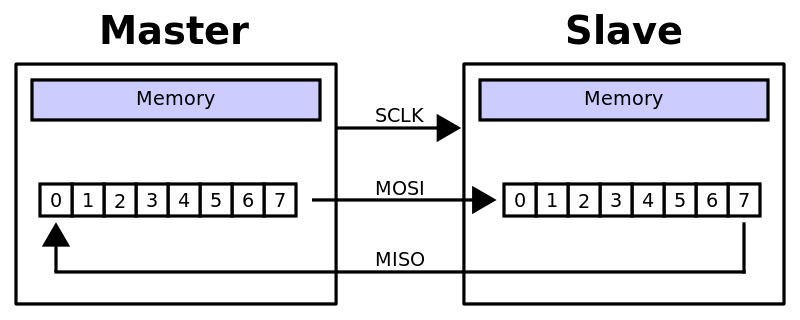

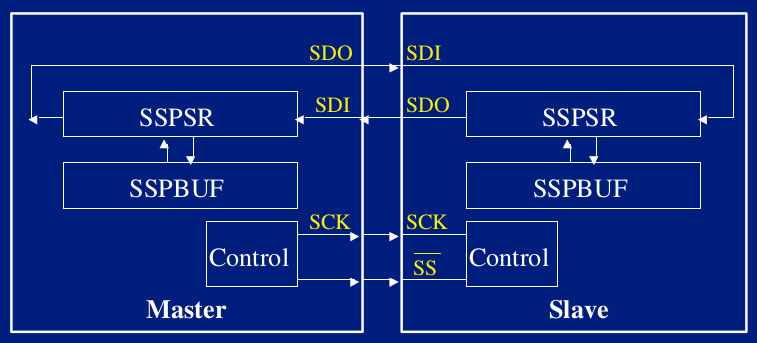

During each SPI clock cycle, a full duplex data transmission occurs. The master sends a bit on the MOSI line and the slave reads it, while the slave sends a bit on the MISO line and the master reads it. This sequence is maintained even when only one-directional data transfer is intended.

Transmissions normally involve two shift registers of some given word size, such as eight bits, one in the master and one in the slave; they are connected in a virtual ring topology. Data is usually shifted out with the most-significant bit first, while shifting a new least-significant bit into the same register. At the same time, data from the counterpart is shifted into the least-significant bit register. After the register bits have been shifted out and in, the master and slave have exchanged register values. If more data needs to be exchanged, the shift registers are reloaded and the process repeats. Transmission may continue for any number of clock cycles. When complete, the master stops toggling the clock signal, and typically deselects the slave.

Every slave on the bus that has not been activated using its chip select line must disregard the input clock and MOSI signals, and must not drive MISO.

SPI Configuration

Because there is no official specification, what exactly SPI is and what not, it is necessary to consult the data sheets of the components one wants to use. Important are the permitted clock frequencies and the type of valid transitions.

Peripheral Types

Peripheral types can be subdivided into the following categories:

- Converters (ADC and DAC)

- Memories (EEPROM and FLASH)

- Real Time Clocks (RTC)

- Sensors (temperature, pressure)

- Others (signalmixer, potentiometer, LCD controller, UART, CAN controller, USB controller, amplifier)

The Peripheral Manufacturer List and Peripheral Device List can be found on website:

References

- Serial Buses Information Page

- SPI - Serial Peripheral Interface

- SPI Interface

- SPI - Overview and Use of the PICmicro Serial Peripheral Interface

- Maxim

- 玩转SPI通信接口