RISC-V: The Free and Open RISC Instruction Set Architecture

This article introduces the free and open RISC instruction set architecture RISC-V.

Overview

RISC-V (pronounced risk-five) is an open instruction set architecture (ISA) based on established reduced instruction set computing (RISC) principles.

In contrast to most ISAs, the RISC-V ISA can be freely used for any purpose, permitting anyone to design, manufacture and sell RISC-V chips and software. While not the first open ISA, it is significant because it is designed to be useful in modern computerized devices such as warehouse-scale cloud computers, high-end mobile phones and the smallest embedded systems. Such uses demand that the designers consider both performance and power efficiency. The instruction set also has a substantial body of supporting software, which fixes a usual weakness of new instruction sets.

The project began in 2010 at the University of California, Berkeley, but many contributors are volunteers and industry workers outside the university.

The RISC-V ISA has been designed with small, fast, and low-power real-world implementations in mind, but without over-architecting for a particular microarchitecture style.

RISC-V Specifications

As of May 2017, version 2.2 of the user-space ISA is fixed and the privileged ISA is available as draft version 1.10.

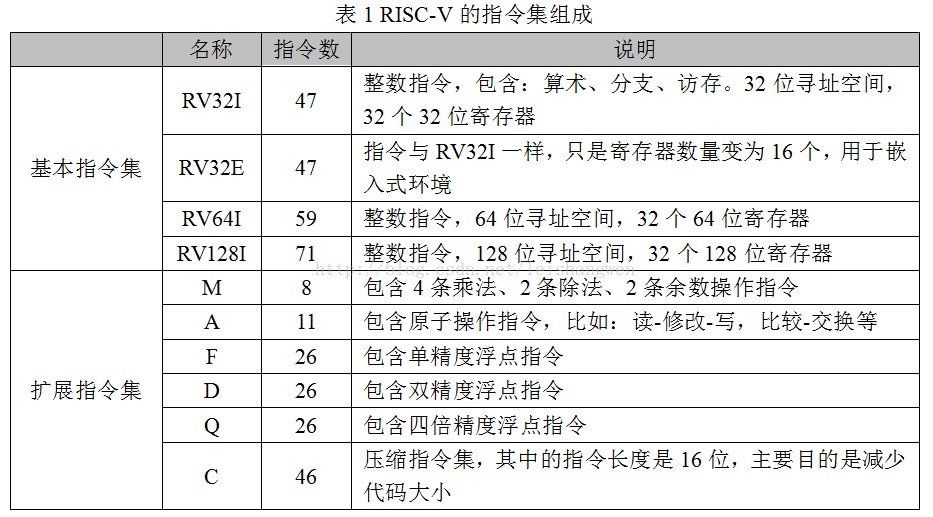

RISC-V Instruction Set:

References

- RISC-V Foundation

- RISC-V Specifications

- RISC-V Software Ecosystem Overview

- RISC-V Genealogy Report

- RISC-V Instruction Lineage Poster v6

- RISC-V Instruction Set

- RISC-V on Wikipedia

- RISC-V双周简报