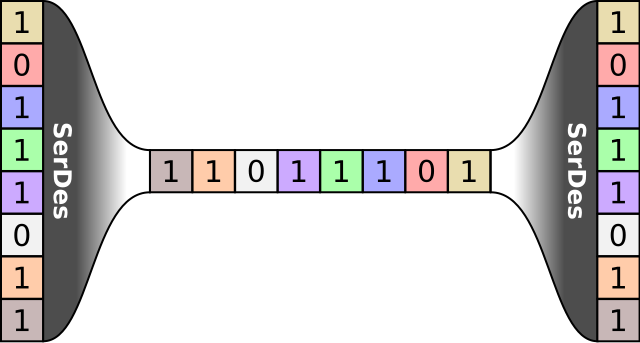

SerDes: Serializer/Deserializer

This article introduces the SerDes (Serializer/Deserializer).

Overview

A Serializer/Deserializer (SerDes) is a pair of functional blocks commonly used in high speed communications to compensate for limited input/output. These blocks convert data between serial data and parallel interfaces in each direction. The term SerDes generically refers to interfaces used in various technologies and applications. The primary use of a SerDes is to provide data transmission over a single/differential line in order to minimize the number of I/O pins and interconnects.

SerDes chips facilitate the transmission of parallel data between two points over serial streams, reducing the number of data paths and thus the number of connecting pins or wires required. Most SerDes devices are capable of full-duplex operation, meaning that data conversion can take place in both directions simultaneously. SerDes chips are used in Gigabit Ethernet systems, wireless network routers, fiber optic communications systems, and storage applications. Specifications and speeds vary depending on the needs of the user and on the application. Some SerDes devices are capable of operating at speeds in excess of 10 Gbps.

Generic Function

The basic SerDes function is made up of two functional blocks: the Parallel In Serial Out (PISO) block (aka Parallel-to-Serial converter) and the Serial In Parallel Out (SIPO) block (aka Serial-to-Parallel converter). There are 4 different SerDes architectures (Also see SerDes Architectures and Applications):

The PISO (Parallel Input, Serial Output) block typically has a parallel clock input, a set of data input lines, and input data latches. It may use an internal or external phase-locked loop (PLL) to multiply the incoming parallel clock up to the serial frequency. The simplest form of the PISO has a single shift register that receives the parallel data once per parallel clock, and shifts it out at the higher serial clock rate. Implementations may also make use of a double-buffered register to avoid metastability when transferring data between clock domains.

The SIPO (Serial Input, Parallel Output) block typically has a receive clock output, a set of data output lines and output data latches. The receive clock may have been recovered from the data by the serial clock recovery technique. However, SerDes which do not transmit a clock use reference clock to lock the PLL to the correct Tx frequency, avoiding low harmonic frequencies present in the data stream. The SIPO block then divides the incoming clock down to the parallel rate. Implementations typically have two registers connected as a double buffer. One register is used to clock in the serial stream, and the other is used to hold the data for the slower, parallel side.

Some types of SerDes include encoding/decoding blocks. The purpose of this encoding/decoding is typically to place at least statistical bounds on the rate of signal transitions to allow for easier clock recovery in the receiver, to provide framing, and to provide DC balance.

Parallel clock SerDes

Parallel clock SerDes is normally used to serialize a parallel bus input along with data address & control signals. The serialized stream is sent along with a reference clock. The clock jitter tolerance at the serializer is 5-10 ps rms.

Embedded clock SerDes

An embedded clock SerDes serializes data and clock into a single stream. One cycle of clock signal is transmitted first, followed by the data bit stream; this creates a periodic rising edge at the start of the data bit stream. As the clock is explicitly embedded and can be recovered from the bit stream, the serializer (transmitter) clock jitter tolerance is relaxed to 80-120 ps rms, while the reference clock disparity at the deserializer can be +/-50000 ppm (i.e. 5%).

8b/10b SerDes

8b/10b SerDes maps each data byte to a 10bit code before serializing the data. The deserializer uses the reference clock to monitor the recovered clock from the bit stream. As the clock information is synthesized into the data bit stream, rather than explicitly embedding it, the serializer (transmitter) clock jitter tolerance is to 5-10 ps rms and the reference clock disparity at the deserializer is +/-100ppm.

A common coding scheme used with SerDes is 8b/10b encoding. This supports DC-balance, provides framing, and guarantees frequent transitions. The guaranteed transitions allow a receiver to extract the embedded clock. The control codes allow framing, typically on the start of a packet. The typical 8b/10b SerDes parallel side interfaces have one clock line, one control line and 8 data lines.

Such serializer-plus-8b/10b encoder, and deserializer-plus-decoder blocks are defined in the Gigabit Ethernet specification.

Another common coding scheme used with SerDes is 64b/66b encoding. This scheme statistically delivers DC-balance and transitions through the use of a scrambler. Framing is delivered through the deterministic transitions of the added framing bits.

Such serializer-plus-64b/66b encoder and deserializer-plus-decoder blocks are defined in the 10 Gigabit Ethernet specification. The transmit side comprises a 64b/66b encoder, a scrambler, and a gearbox that converts the 66b signal to a 16 bit interface. Another serializer then converts this 16 bit interface into a fully serial signal.

Bit interleaved SerDes

Bit interleaved SerDes multiplexes several slower serial data streams into faster serial streams, and the receiver demultiplexes the faster bit streams back to slower streams.

Standardization of SerDes

The Optical Internetworking Forum (OIF) has published the Common Electrical I/O (CEI) Interoperability Agreements (IAs), that have defined 5 generations of the electrical interface of SerDes, at 3.125, 6, 10, 28 and 56 Gb/s. The OIF has announced new projects at 112 Gb/s. The OIF also published three earlier generations of electrical interfaces. These IAs have been adopted or adapted or have influenced high speed electrical interfaces defined by IEEE 802.3, Infiniband, RapidIO, Fibre Channel and numerous other bodies.

- OIF-OFP-01.0 – OTN Over Packet Fabric Protocol (OFP) Implementation Agreement (November 2011)

- OIF-MLG-01.0 – Multi-link Gearbox Implementation Agreement (May 2012)

- OIF-MLG-02.0 – Multi-link Gearbox Implementation Agreement (April 2013)

- OIF-MLG-03.0 – Multi-link Gearbox Implementation Agreement (March 2016)

- OIF-FLEXE-01.0 – Flex Ethernet Implementation Agreement (March 2016)

- OIF-FLEXE-01.1 – Flex Ethernet Implementation Agreement (June 2017)

References

- SerDes on en.wikipedia.org

- Optical Internetworking Forum (OIF)

- SerDes Architectures and Applications