CPRI: Common Public Radio Interface

This article introduces the Common Public Radio Interface (CPRI) used in Radio Base Station (RBS).

CPRI

CPRI Introduction

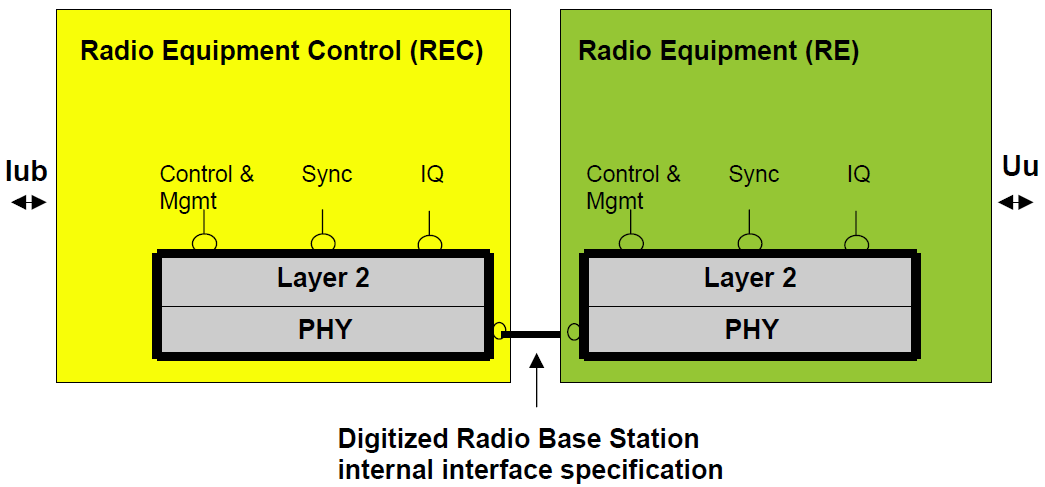

The Common Public Radio Interface (CPRI) is an industry cooperation aimed at defining a publicly available specification for the key internal interface of Radio Base Stations (RBS) between the Radio Equipment Control (REC) and the Radio Equipment (RE). The Parties cooperating to define the CPRI Specification and are now encompassing Ericsson, Huawei, NEC and Nokia. Nortel contributed as member of the CPRI cooperation to CPRI Specification versions 1.4, 2.1, 3.0, 4.0 and 4.1 and left the cooperation in December 2009.

Refer to the following documents for more information:

- CPRI Roadmap

- Introduction to CPRI

- Understanding the Basics of CPRI Fronthaul Technology

- An Overview of the CPRI Specification and Its Application to C-RAN-Based LTE Scenarios

CPRI Releases

The following table shows CPRI releases:

| Rel | Release_Date | Supported Specs |

|---|---|---|

| v1.0 | 2003-09-30 | 3GPP UTRA FDD Rel. 5 |

| v1.1 | 2004-05-10 | 3GPP UTRA FDD Rel. 5 |

| v1.2 | 2004-07-15 | 3GPP UTRA FDD Rel. 5 |

| v1.3 | 2004-10-01 | 3GPP UTRA FDD Rel. 5 |

| v2.0 | 2004-10-01 | 3GPP UTRA FDD Rel. 5 |

| v1.4 | 2006-03-31 | 3GPP UTRA FDD Rel. 6 |

| v2.1 | 2006-03-31 | 3GPP UTRA FDD Rel. 6 |

| v3.0 | 2006-10-20 | 3GPP UTRA FDD Rel. 6 WIMAX Forum Mobile System Profile v1.1.0 |

| v4.0 | 2008-06-30 | 3GPP UTRA FDD Rel. 8 3GPP E-UTRA Rel. 8 WIMAX Forum Mobile System Profile v1.1.0 |

| v4.1 | 2009-02-18 | 3GPP UTRA FDD Rel. 8 3GPP E-UTRA Rel. 8 WiMAX Forum Mobile System Profile Release 1.0 Approved Specification (Revision 1.7.1, 2008-11-07) |

| v4.2 | 2010-09-29 | 3GPP UTRA FDD Rel. 9 3GPP E-UTRA Rel. 9 WiMAX Forum Mobile System Profile Release 1.5 Approved Specification (2009-08-01) |

| v5.0 | 2011-09-21 | 3GPP UTRA FDD Rel. 9 3GPP E-UTRA Rel. 9 3GPP GERAN Rel. 9 WiMAX Forum Mobile System Profile Release 1.5 Approved Specification (2009-08-01) |

| v6.0 | 2013-08-30 | 3GPP UTRA FDD Rel. 10 3GPP E-UTRA Rel. 10 3GPP GERAN Rel. 10 WiMAX Forum Mobile System Profile Release 1.5 Approved Specification (2009-08-01) |

| v6.1 | 2014-07-01 | 3GPP UTRA FDD Rel. 10 3GPP E-UTRA Rel. 10 3GPP GERAN Rel. 10 WiMAX Forum Mobile System Profile Release 1.5 Approved Specification (2009-08-01) |

| v7.0 | 2015-10-09 | 3GPP UTRA FDD Rel. 10 3GPP E-UTRA Rel. 10 3GPP GERAN Rel. 10 WiMAX Forum Mobile System Profile Release 1.5 Approved Specification (2009-08-01) |

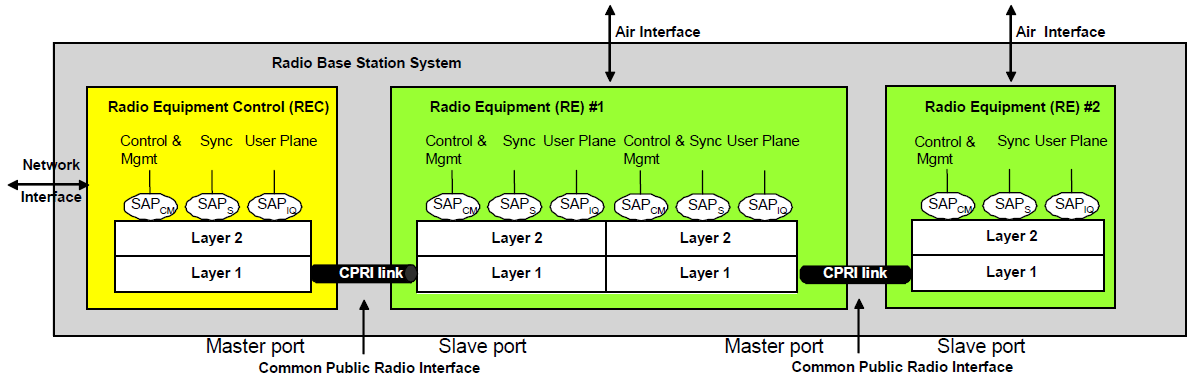

CPRI System Architecture

The following figures show the basic system architecture and CPRI definition, refer to REC and RE Description:

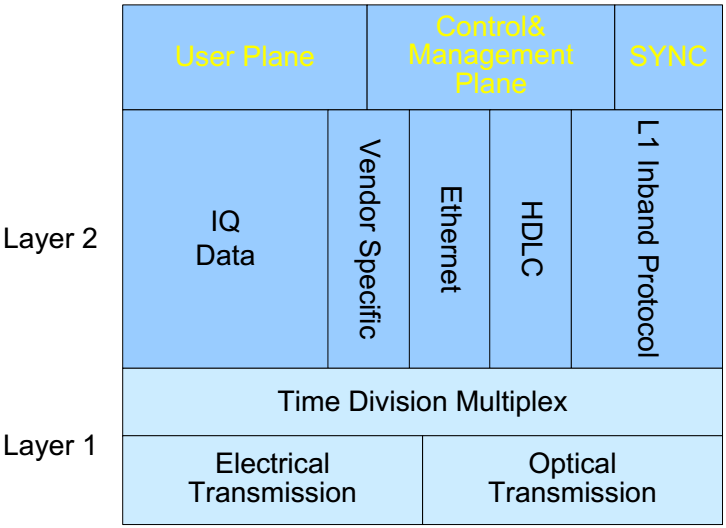

The scope of CPRI specifications:

-

User Plane data, Control Plane transport mechanisms, and means for synchronisation

- User Plane: Data that has to be transferred from the Radio Base Station (RBS) to the Mobile Station (MS), and vice versa.

- Control Plane: Control data flow used for call processing.

- Management Plane: This data is management information for the operation, administration and maintenance of the CPRI link and the nodes.

- Synchronization: Data flow which transfers synchronization and timing information between nodes (RECs, REs).

-

Cover Layers 1 and 2 of OSI stack

-

The physical layer (layer 1) will support both an electrical interface (i.e. what is used in traditional base stations), and an optical interface (e.g. for base stations with remote radio equipment). It defines:

- Electrical characteristics

- Optical characteristics

- Time division multiplexing of the different data flows

- Low level signalling

-

The data link layer (layer 2) shall support flexibility and scalability. It defines:

- Media access control

- Flow control

- Data protection of the control and management information flow

-

In addition to the user plane data (IQ data), control and management as well as synchronization signals have to be exchanged between the REC and the RE. All information flows are multiplexed onto a digital serial communication line using appropriate layer 1 and layer 2 protocols. The different information flows have access to the layer 2 via appropriate Service Access Points (SAP).

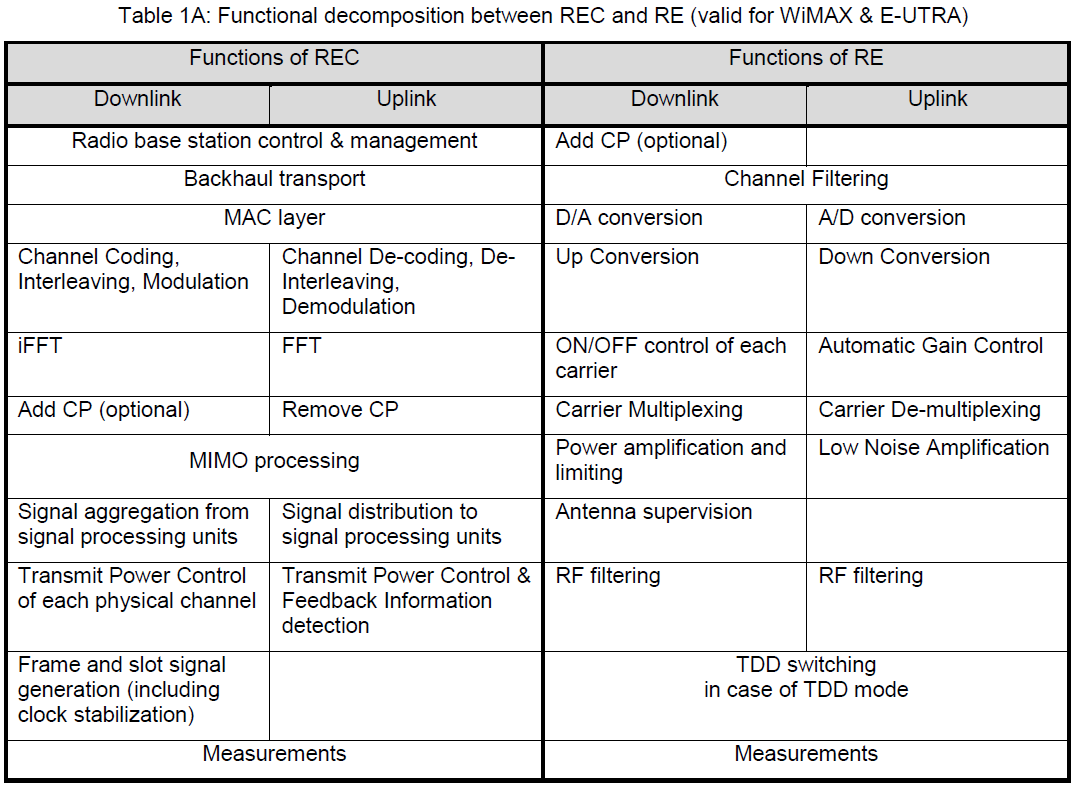

Functional Decomposition

The REC is concerned with the Network Interface transport, the radio base station control and management as well as the digital baseband processing. The RE provides the analogue and radio frequency functions such as filtering, modulation, frequency conversion and amplification.

The following figure shows the functional decomposition between REC and RE for WiMAX & E-UTRA:

CPRI Protocol Overview

The CPRI specification will cover Layers 1 and 2 of the OSI stack:

- The physical layer (layer 1) will support both an electrical interface (i.e. what is used in traditional base stations), and an optical interface (e.g. for base stations with remote radio equipment).

- The data link layer (layer 2) shall support flexibility and scalability.

CPRI defines the layer 1 and layer 2 protocols for the transfer of user plane, C&M as well as synchronization information between REC and RE as well as between two REs. The interface supports the following types of information flows:

- IQ Data: User plane information in the form of in-phase (I) and quadrature (Q) modulation data (digital baseband signals). The IQ data of different antenna carriers are multiplexed by a time division multiplexing scheme onto an electrical or optical transmission line.

- Synchronization: Synchronization data used for frame and time alignment.

- L1 Inband Protocol: Signalling information that is related to the link and is directly transported by the physical layer. This information is required, e.g. for system start-up, layer 1 link maintenance and the transfer of time critical information that has a direct time relationship to layer 1 user data.

- C&M data: Control and management information exchanged between the control and management entities within the REC and the RE. This information flow is given to the higher protocol layers.

- Protocol Extensions: This information flow is reserved for future protocol extensions. It may be used to support, e.g., more complex interconnection topologies or other radio standards.

- Vendor Specific Information: This information flow is reserved for vendor specific information.

Basic Frame Structure

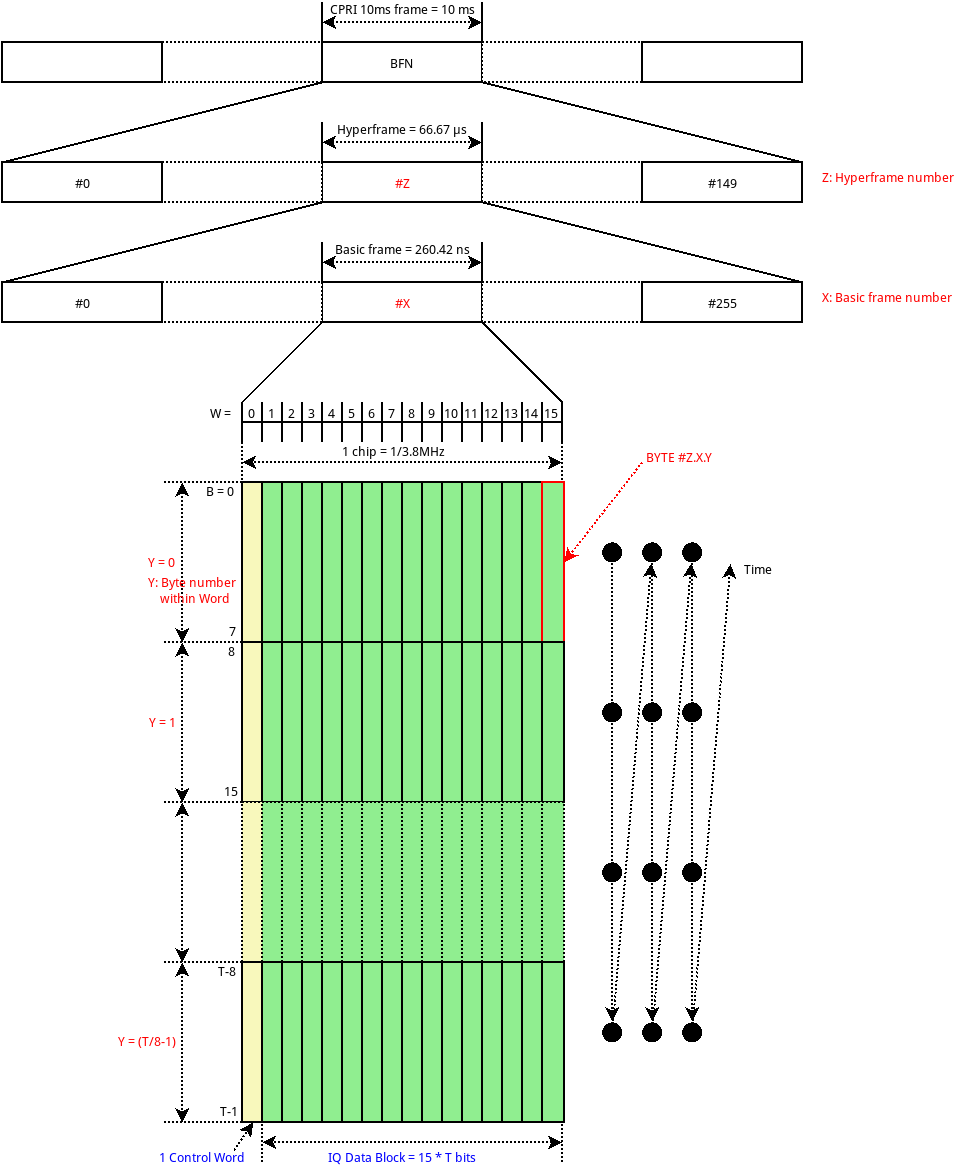

The following figure is illustration of the frame hierarchy and notation indices:

- Z is the hyperframe number within a CPRI 10ms frame

- X is the basic frame number within a hyperframe

- W is the word number within a basic frame

- Y is the byte number within a word

The control word is defined as the first Tcw bits of the word with rank W=0. The value ranges of the indices are shown in below table:

| Opt | Line Bit Rate (Mbit/s) |

Line Coding | Length of Word (bit) |

Length of Control Word (bit) |

Z | X | W | Y | B |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 614.4 (1 x 491.52 x 10/8) |

8b/10b | T=8 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0 | 0, 1, .., 7 |

| 2 | 1228.8 (2 x 491.52 x 10/8) |

8b/10b | T=16 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1 | 0, 1, .., 15 |

| 3 | 2457.6 (4 x 491.52 x 10/8) |

8b/10b | T=32 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, 3 | 0, 1, .., 31 |

| 4 | 3072.0 (5 x 491.52 x 10/8) |

8b/10b | T=40 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, 3, 4 | 0, 1, .., 39 |

| 5 | 4915.2 (8 x 491.52 x 10/8) |

8b/10b | T=64 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 7 | 0, 1, .., 63 |

| 6 | 6144.0 (10 x 491.52 x 10/8) |

8b/10b | T=80 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 9 | 0, 1, .., 79 |

| 7 | 8110.08 (16 x 491.52 x 10/8) |

8b/10b | T=128 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 15 | 0, 1, .., 127 |

| 7A | 9830.4 (16 x 491.52 x 66/64) |

64b/66b | T=128 | Tcw=T | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 15 | 0, 1, .., 127 |

| 8 | 10137.6 (20 x 491.52 x 66/64) |

64b/66b | T=160 | Tcw=128 | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 19 | 0, 1, .., 159 |

| 9 | 12165.12 (24 x 491.52 x 66/64) |

64b/66b | T=192 | Tcw=128 | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 23 | 0, 1, .., 191 |

| 10 | 24330.24 (48 x 491.52 x 66/64) |

64b/66b | T=384 | Tcw=128 | 0, 1, .., 149 | 0, 1, .., 255 | 0, 1, .., 15 | 0, 1, 2, .., 47 | 0, 1, .., 383 |

Take line bit rate 2457.6 Mbit/s for instance:

- Number of bits per basic frame = 4 bytes within one word * 16 words * 32 bits per word = 512 bits

- Frequency of basic frame = 3.84 MHz

so, the line bit rate is derived by:

512 bits * 3.84MHz * 10/8 = 4 * 491.52 * 10/8 = 2457.6 Mbit/s

The frequency of basic frame is derived by:

256 * 150 / (10ms) = 3.84MHz

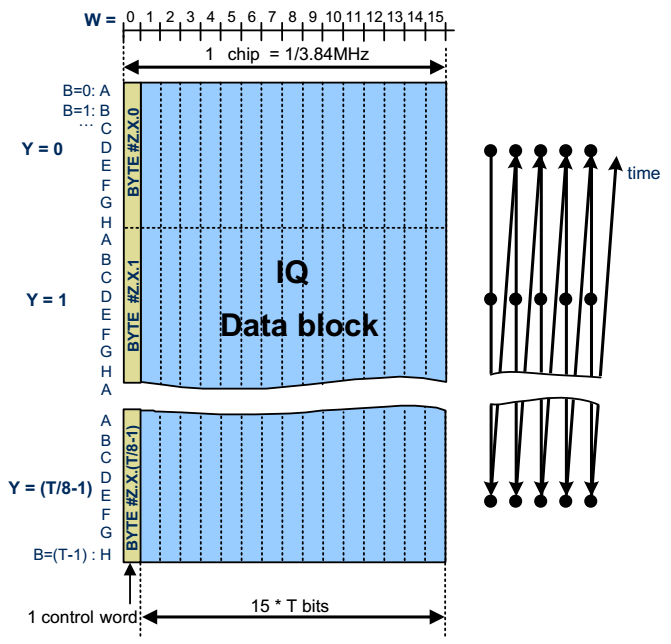

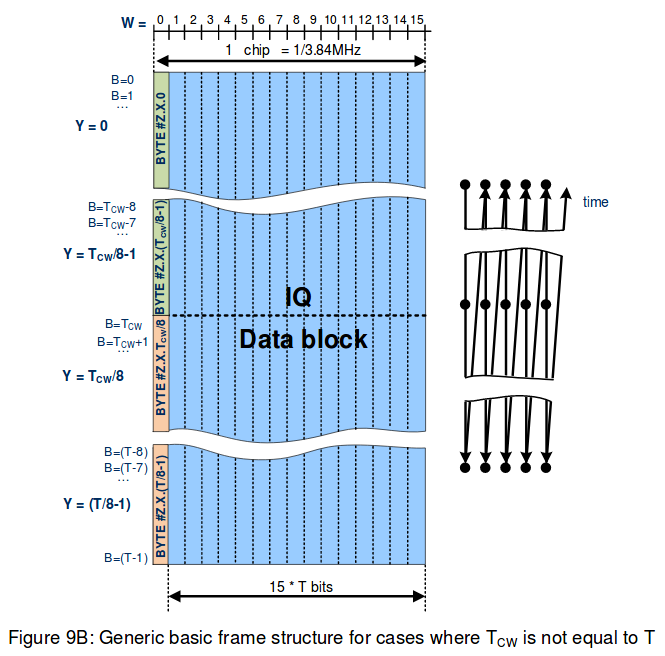

The length of a basic frame is 1 Tchip = 1/fchip = 1/3.84 MHz = 260.42 ns. A basic frame consists of 16 words with index W=0..15. The length T of the word depends on the CPRI line bit rate. Each bit within a word is addressed with the index B, where B=0 is the LSB and B=T-1 is the MSB. Each BYTE within a word is addressed with the index Y, where B=0 is LSB of Y=0, B=7 is MSB of Y=0, B=8 is LSB of Y=1, etc.

The following figure shows basic frame structure, where Tcw = T:

The following figure shows basic frame structure, where Tcw ≠ T:

As shown in above two figures, the control BYTES of one basic frame are always transmitted first.

8b/10b Line Coding

In telecommunications, 8b/10b is a line code that maps 8-bit words to 10-bit symbols to achieve DC-balance and bounded disparity, and yet provide enough state changes to allow reasonable clock recovery. This means that the difference between the counts of ones and zeros in a string of at least 20 bits is no more than two, and that there are not more than five ones or zeros in a row. This helps to reduce the demand for the lower bandwidth limit of the channel necessary to transfer the signal.

An 8b/10b code can be implemented in various ways, where the design may focus on specific parameters such as hardware requirements, DC-balance, etc. One implementation was designed by K. Odaka for the DAT digital audio recorder. Kees Schouhamer Immink designed an 8b/10b code for the DCC audio recorder. The IBM implementation was described in 1983 by Al Widmer and Peter Franaszek.

As the scheme name suggests, eight bits of data are transmitted as a 10-bit entity called a symbol, or character. The low five bits of data are encoded into a 6-bit group (the 5b/6b portion) and the top three bits are encoded into a 4-bit group (the 3b/4b portion). These code groups are concatenated together to form the 10-bit symbol that is transmitted on the wire.

Refer to 8b/10b encoding for more information.

64b/66b Line Coding

In data networking and transmission, 64b/66b is a line code that transforms 64-bit data to 66-bit line code to provide enough state changes to allow reasonable clock recovery and facilitate alignment of the data stream at the receiver. It was defined by the IEEE 802.3 working group as part of the IEEE 802.3ae-2002 amendment which introduced 10 Gbit/s Ethernet.

The Protocol overhead of a coding scheme is the ratio of the number of added coding bits to the number of raw payload bits. The overhead of 64b/66b encoding is 2 overhead bits for every 64 raw bits transmitted or 3.125%. This is considerably more efficient than the 25% overhead of the previously used 8b/10b encoding scheme which essentially charges every 8 bits of source data with a 2 bit (or 25%) tax. At the time 64b/66b was deployed, it allowed 10 Gb Ethernet to be transmitted with the same lasers used by SONET OC-192, rather than requiring 12.5 Gbit/s lasers, which were not expected to become available for several years.

The overhead can be reduced further by doubling the block size to produce 128b/130b encoding, as used by PCIe 3.0, and a very similar variant is the 128b/132b encoding used by USB 3.1.

Refer to 64b/66b encoding and section 6.7 of CPRI Specification v7.0.

Control Words

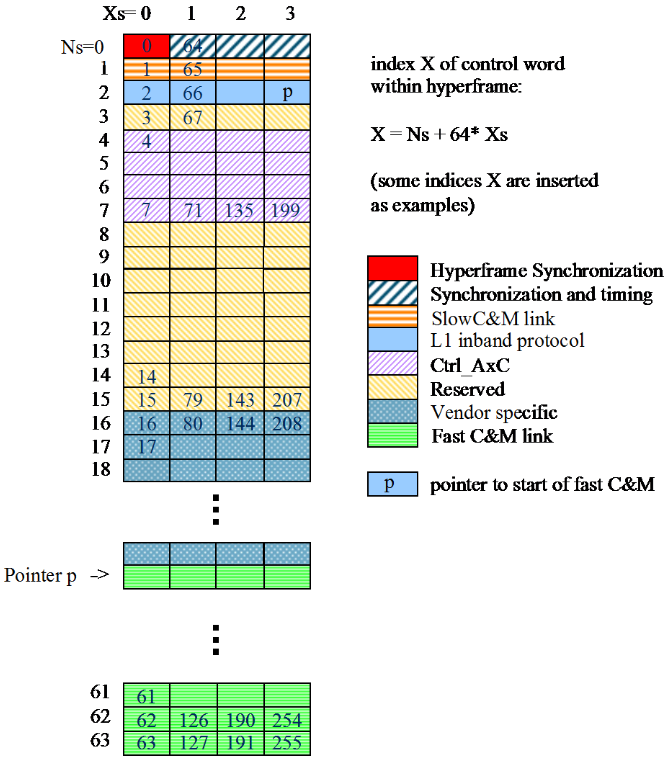

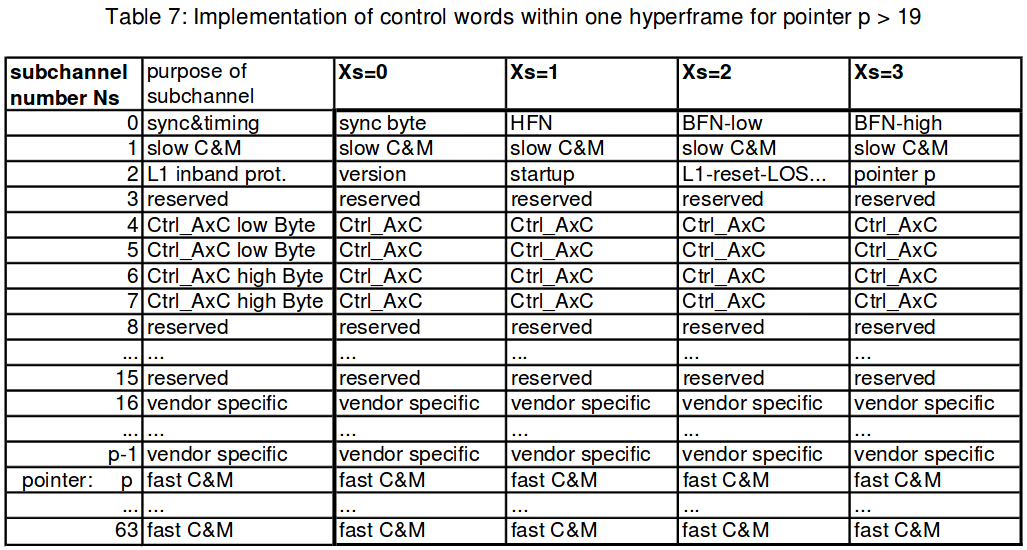

The 256 control words of a hyperframe are organized into 64 subchannels of 4 control words each. One subchannel contains 4 control words per hyperframe.

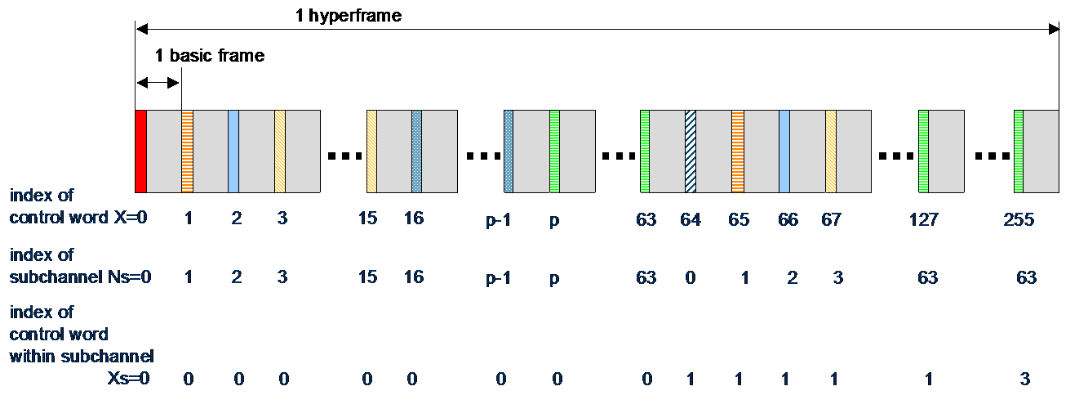

The index Ns of the subchannel ranges from 0 to 63. The index Xs of a control word within a subchannel has four possible values, namely 0, 1, 2 and 3. The index X of the control word within a hyperframe is given by X = Ns + 64*Xs.

The following figure is illustration of control words and subchannels within one hyperframe:

The following figure is illustration of subchannels within one hyperframe:

The following figure is implementation of control words within one hyperframe:

Synchronization Data

| BYTE index | Function |

|---|---|

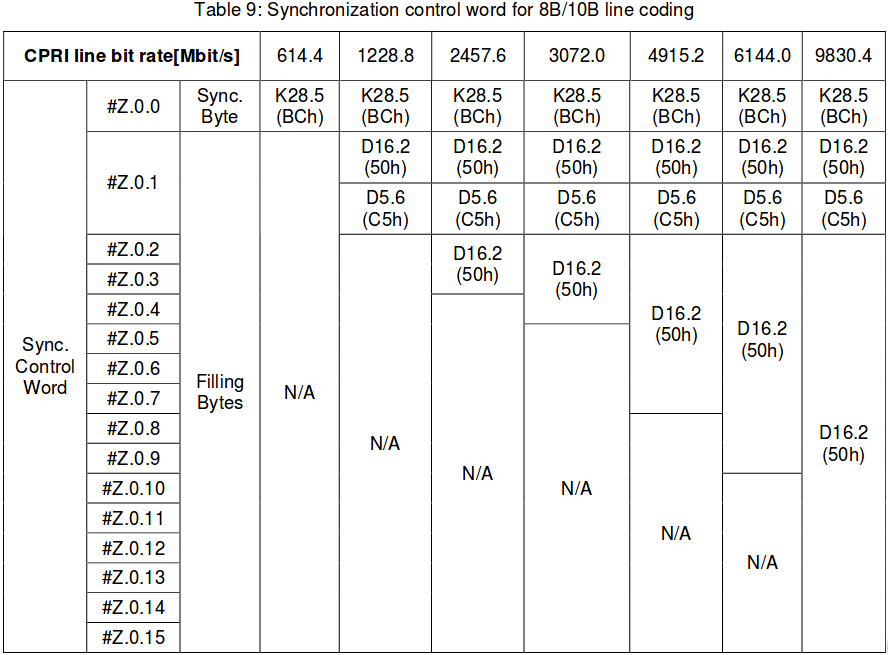

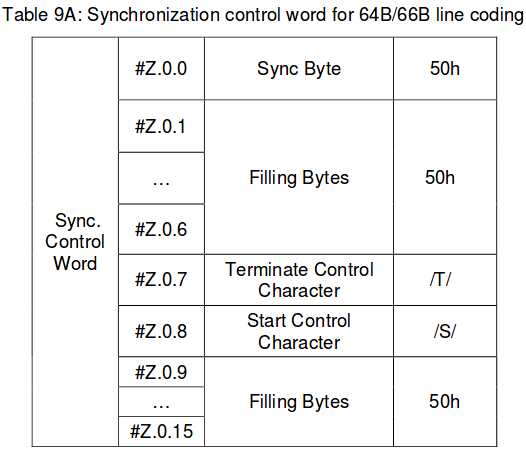

| Z.0.0 | Start of hyperframe (Sync Byte). The content is Special code K28.5 (8B/10B line coding, see Table 9), 50h (64B/66B line coding, see Table 9A) |

| Z.64.0 | HFN (HyperFrame Number), HFN=0..149, the first hyperframe in an UMTS radio frame has HFN=0. |

| Z.128.0 Z.192.0 |

BFN (CPRI 10ms Frame Number; for UTRA FDD aligned with NodeB Frame Number). #Z.128.0 (low byte) and b3-b0 of #Z.192.0 are BFN. b7-b4 of #Z.192.0 are reserved. |

The RE shall use the incoming bit clock at the slave port where the SAPs is assigned as the source for the radio transmission and any link transmission bit clock. The time information is transferred from the REC to the RE through the information described here. The CPRI 10ms frame delimitation is provided by the Sync Byte (#Z.0.0) of the hyperframe number #0.

For UMTS frame timing, the UMTS radio frame is identical to the CPRI 10ms frame, where the term UMTS radio frame is used for the UTRA FDD 10ms frame as well as for the E-UTRA 10ms frame.

For WiMAX frame timing and GSM frame timing, refer to section 4.2.8 of CPRI Specification v7.0 for more details.

C&M Plane Data Channels

CPRI supports two different types of C&M channels, which shall be selected from the following option list:

- C&M Channel Option 1: Slow C&M Channel based on HDLC

- C&M Channel Option 2: Fast C&M Channel based on Ethernet

The use of either HDLC or Ethernet is optional. It is recommended for each REC or RE to support at least one non-zero C&M channel bit rate on at least one link.

A passive link does not support any C&M channel. It may be requested by the master port indicating #Z.66.0 = rrrr r000 and #Z.194.0 = rr00 0000 (r = reserved, transmit 0, receiver don’t care) in downlink.

Slow C&M Channel

One option is to use a low rate HDLC channel for C&M data. The bit rate is defined by the 3 LSBs of the “start-up information” BYTE #Z.66.0, refer to L1 Inband Protocol. Also refer to section 4.2.7.7.1 and 4.3 of CPRI Specification v7.0 for more details.

Fast C&M Channel

Another option is to use a high data rate Ethernet Channel which can be flexibly configured by the pointer in control BYTE #Z.194.0. The mapping of the Ethernet data follows the same principle as the HDLC channel (no byte alignment, LSB first). Also refer to section 4.2.7.7.2 and 4.4 of CPRI Specification v7.0 for more details.

L1 Inband Protocol

| BYTE index | Function |

|---|---|

| Z.2.0 | Protocol version: “0000 0001” or “0000 0010” for version 1 and 2 respectively |

| Z.66.0 | Start-up. Format: “rrrr rCCC”, where b2-b0 HDLC bit rate and b7-b3: reserved. For b2-b0: 000: no HDLC 001: 240kbit/s HDLC 010: 480kbit/s HDLC 011: 960kbit/s HDLC (for line bit rates ≥ 1228.8Mbit/s) 100: 1920kbit/s HDLC (for line bit rates ≥ 2457.6Mbit/s) 101: 2400kbit/s HDLC (for line bit rates ≥ 3072.0Mbit/s) 110: Highest possible HDLC bit rate (for line bit rates > 3072.0Mbit/s) 111: HDLC bit rate negotiated on higher layer. |

| Z.130.0 | Basic layer 1 functions: Reset (see below) RAI (Remote Alarm Indication) L1 SDI (SAP Defect Indication) LOS (Loss of Signal) LOF (Loss of Frame) Format: “rrrF LSAR”, where: b0: Reset b1: RAI (see 4.2.10.4 of CPRI Specification v7.0) b2: SDI (see 4.2.10.5 of CPRI Specification v7.0) b3: LOS (see 4.2.10.2 of CPRI Specification v7.0) b4: LOF (see 4.2.10.3 of CPRI Specification v7.0) b7-b5: reserved |

| Z.194.0 | Pointer p, which indicates the subchannel number Ns at which the control words for the Ethernet channel starts within a hyperframe. Format: “rrPPPP PP”, where: b5-b0: Pointer to subchannel number b7-b6: reserved |

Reset

Reset of the link is managed through start-up sequence definition. Reset of the RE is managed with the Reset bit in #Z.130.0. The reset notification can only be sent from a master port to a slave port. The reset acknowledgement can only be sent from a slave port to a master port. When the master wants to reset a slave, it shall set DL #Z.130.0 b0 for at least 10 hyperframes. On the reception of a valid reset notification, the slave shall set UL #Z.130.0 b0 at least 5 hyperframes on the same link.

When an RE receives a valid reset notification on any of its slave ports, it shall not only reset itself, but also forward reset notification on all its master ports by setting DL #Z.130.0 b0 for at least 10 hyperframes.

While in reset and if the link is still transmitting, the RE must set the SDI bit.

Future Protocol Extensions

There are 36 control words of one hyperframe reserved for future interface protocol extensions. Reserved words are completely filled with reserved bits (reserved bits are marked with r). This means that a transmitter shall send 0’s for bits marked with r, and the receiver shall not interpret bits marked with r (transmit: r = 0, receiver: r = don’t care).

Control AxC Data

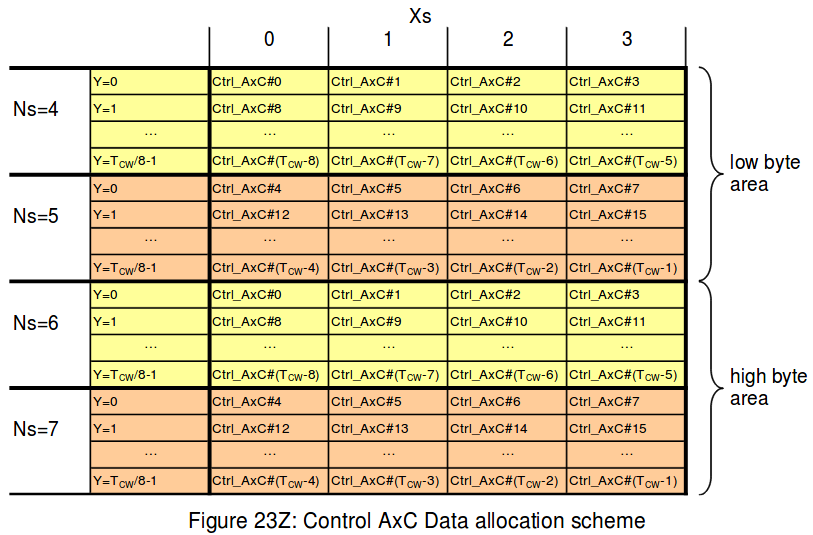

Up to 16 control words (in subchannels 4 to 7) of one hyperframe are available for AxC specific control data. In each hyperframe AxC specific Control Data streams (Ctrl_AxC) with dedicated numbers Ctrl_AxC# are allocated with a granularity of two bytes according to the following rule:

- Low byte

Ctrl_AxC# = Y*8 + Xs + (Ns - 4)*4, with Ns ∈ {4, 5}

- High byte

Ctrl_AxC# = Y*8 + Xs + (Ns - 6)*4, with Ns ∈ {6, 7}

with

Y = 0, .., Tcw/8-1

Xs = 0, .., 3

The resulting allocation scheme is shown in the following figure. Tcw x 2 bytes are reserved per hyperframe with parameter Tcw.

The mapping of Ctrl_AxC with number Ctrl_AxC# to AxCs is not defined in CPRI but is vendor specific. The same applies for the actual content of the control data bytes.

The given Control AxC Data scheme is one possibility to transmit associated AxC specific control data in GSM (e.g. GSM frequency hopping information), but may be also used for other purposes, e.g. real time RTWP measurement reporting in UMTS.

Vendor Specific Data

Depending on the usage of the fast C&M channel, up to 192 control words (in subchannels 16 to 63) of one hyperframe are available for vendor specific data. A minimum of 16 control words (in subchannels 16 to 19) per hyperframe are reserved for vendor specific data.

IQ Data Block

IQ Capacity

An AxC Container is a sub-part of the IQ data block of one basic frame. The size of an AxC Container is always an even number of bits. The mapping of AxC Containers into the basic frame is specified in section 4.2.7.2.3 of CPRI Specification v7.0.

| Options | Line Bit Rate (Mbit/s) | Line Coding | Total bits per Basic Frame (bits) | IQ bits per Basic Frame (bits) | No. AxC Container (20bit) | No. AxC Container (24bit) | No. AxC Container (30bit) |

|---|---|---|---|---|---|---|---|

| 1 | 614.4 | 8b/10b | 128 | 120 | 6 | 5 | 4 |

| 2 | 1228.8 | 8b/10b | 256 | 240 | 12 | 10 | 8 |

| 3 | 2457.6 | 8b/10b | 512 | 480 | 24 | 20 | 16 |

| 4 | 3072.0 | 8b/10b | 640 | 600 | 30 | 25 | 20 |

| 5 | 4915.2 | 8b/10b | 1024 | 960 | 48 | 40 | 32 |

| 6 | 6144.0 | 8b/10b | 1280 | 1200 | 60 | 50 | 40 |

| 7 | 8110.08 | 8b/10b | 2048 | 1920 | 96 | 80 | 64 |

| 7A | 9830.4 | 64b/66b | 2048 | 1920 | 96 | 80 | 64 |

| 8 | 10137.6 | 64b/66b | 2560 | 2400 | 120 | 100 | 80 |

| 9 | 12165.12 | 64b/66b | 3072 | 2880 | 144 | 120 | 96 |

| 10 | 24330.24 | 64b/66b | 6144 | 5760 | 288 | 240 | 192 |

Link Delay Accuracy & Cable Delay Calibration

Refer to section 4.2.9 of CPRI Specification v7.0 for more details.

Link Maintenance of Physical Layer

Refer to section 4.2.10 of CPRI Specification v7.0 for more details.

Start-up Sequence

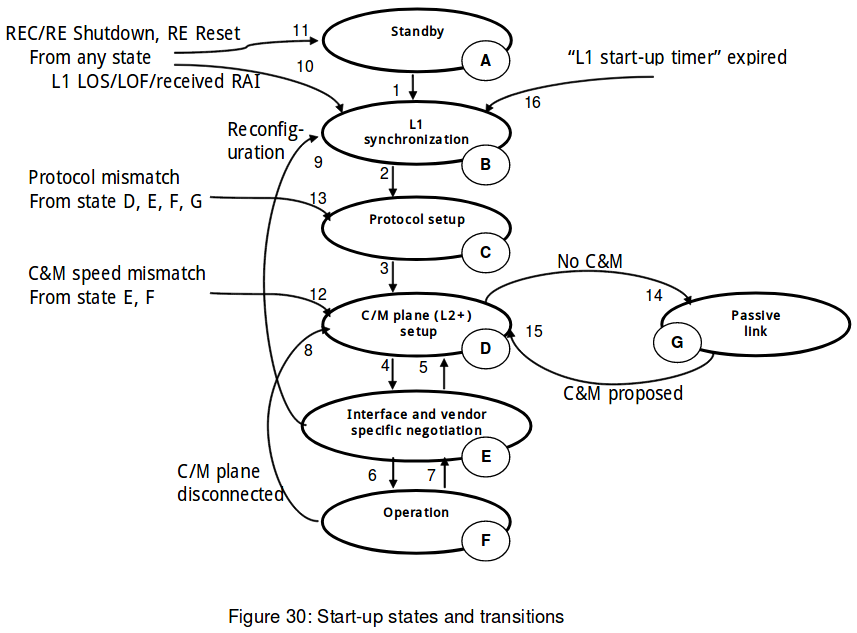

The start-up sequence defines the sequence of actions to be performed by master and slave ports connected by CPRI. When both the slave port and the master port are in state F or G, the link is in normal operation.

After a reset, any configurable ports of the RE shall be configured as slave ports. All ports of the RE shall enter state A. All the master ports of the RE shall remain in state A until at least one of the slave ports has been in state E.

General

The start-up procedure accomplishes two main things:

- Synchronization of layer 1: byte alignment and hyper frame alignment

- Alignment of capabilities of the master and slave ports: line bit rate, protocol, C&M channel bit rate, C&M protocol, vendor specific signalling

Since there is no mandatory line bit rate or C&M channel bit rate the master port and slave port shall, during the start-up procedure, try different configurations until a common match is detected. The common match does not have to be optimal – it shall be considered as just a first contact where capabilities can be exchanged for a proper configuration to be used in the following communication.

For all states, it is mandatory to always transmit information consistent with the protocol indicated in #Z.2.0 on all control words on subchannel 1 and subchannels 3 to 15.

When changing the line bit rate of the transmitted CPRI, the interruption of transmission shall be less than 0.1s. When changing the line bit rate of the received CPRI, the interruption of reception shall be less than 0.1s. The time to reach HFNSYNC for the receiving unit shall be less than 0.2s, given the precondition that the far-end transmitter is on, they use the same line bit rate and no bit errors occur.

In the negotiation steps in state C and D the master and slave ports shall sample and evaluate the received protocol version and C&M channel bit rates at a rate of at least every 0.1s. The transmitted protocol version and C&M channel bit rates shall be updated within 0.2s after the evaluation.

Layer 1 Start-up Timer

The following figure shows the start-up states and transitions, refer to section 4.5.2 and 4.5.3 of CPRI Specification v7.0 for more details.

| States | Means | Decription |

|---|---|---|

| A | Standby | Waiting to be configured to start up CPRI. No transmission or reception of CPRI. |

| B | L1 Synchronization and Rate Negotiation | During this state, the line bit rate of the interface is determined and both master and slave ports reach layer 1 synchronization up to state HFNSYNC. |

| C | Protocol Setup | During this state, a common protocol version of CPRI is determined. |

| D | C&M Plane (L2+) Setup | During this state, a common C&M channel bit rate is determined. |

| E | Interface and Vendor specific Negotiation | During this state, application in master and slave ports negotiate the CPRI usage. |

| F | Operation | Normal operation. |

| G | Passive Link | The interface is not carrying the C&M plane. |

CPRI Interfaces

The physical layer (layer 1) of CPRI specification will support both an electrical interface (i.e. what is used in traditional base stations), and an optical interface (e.g. for base stations with remote radio equipment).

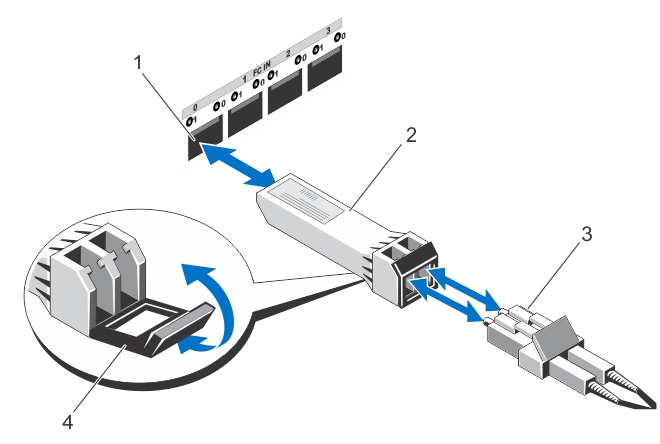

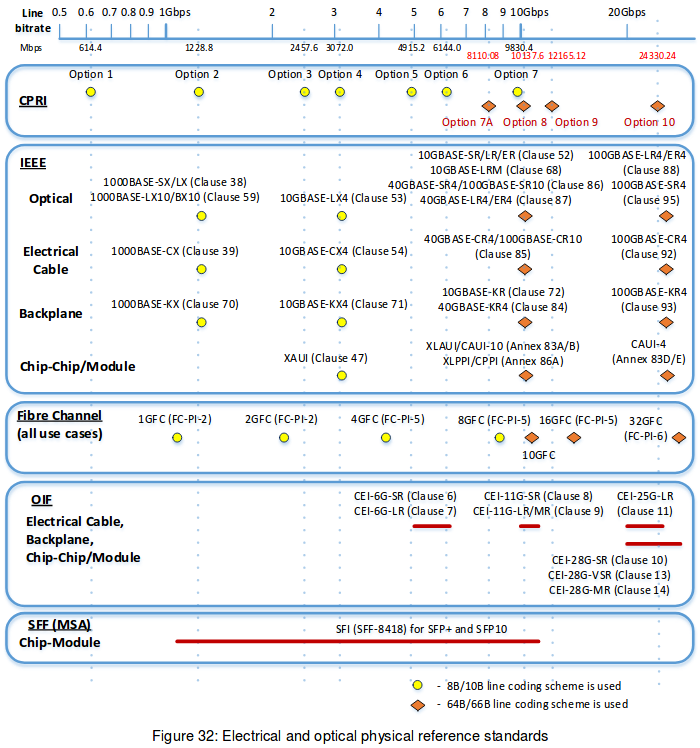

The following figure shows electrical and optical physical reference standards, refer to section 6.2 of CPRI Specification v7.0:

Electrical Interface

-

Electrical Cabling

No specific cabling is recommended by CPRI. The cable performance shall be such that transmitter and receiver performance requirements in section 7.1 of CPRI Specification v7.0 are fulfilled.

-

Electrical Connectors

CPRI electrical implementation may use connector solutions that are described and defined in Fibre Channel Physical Interfaces:

- ANSI/INCITS 404-2006, FC-PI-2, Fibre Channel Physical Interfaces - 2

- ANSI/INCITS 479-2011, FC-PI-5, Fibre Channel Physical Interfaces - 5

- ANSI/INCITS 512-2015, FC-PI-6, Fibre Channel Physical Interfaces - 6

or,

- IEEE Std 802.3-2012 IEEE, New York, USA, 28th December 2012

Optical Interface

-

Optical Cabling

The optical fiber performance shall be such that transmitter and receiver performance requirements in section 7.1 of CPRI Specification v7.0 are fulfilled. The optical fibers recommended for CPRI are:

- IEC 60793-2-10 ed 4.0: Type A1a (50/125 um multimode)

- IEC 60793-2-10 ed 4.0: Type A1b (62.5/125 um multimode)

- IEC 60793-2-10 ed 4.0: Type A1d (100/140 um multimode)

- IEC 60793-2-50 ed 4.0: Type B1, B2, B4, B5, B6 (10/125 um single-mode)

The exception characteristic as specified in IEEE 802.3 Table 38-12 and IEEE 802.3 Table 53-14 as well as ANSI/INCITS 479-2011, FC-PI-5, Fibre Channel Physical Interfaces uC 5 Table 7 and Table 11 as well as ANSI/INCITS 512-2015, FC-PI-6, Fibre Channel Physical Interfaces - 6 Table 8 and Table 10 may be taken into account.

-

Optical Connectors

CPRI optical implementation may use connector solutions that are described and defined in Fibre Channel Physical Interfaces:

- ANSI/INCITS 404-2006, FC-PI-2, Fibre Channel Physical Interfaces - 2

- ANSI/INCITS 479-2011, FC-PI-5, Fibre Channel Physical Interfaces - 5

- ANSI/INCITS 512-2015, FC-PI-6, Fibre Channel Physical Interfaces - 6

or,

- IEEE Std 802.3-2012 IEEE, New York, USA, 28th December 2012

These solutions are known to achieve the performance requirements in section 7.1 of CPRI Specification v7.0. A high flexibility in the choice of connector and transceiver can be achieved by adopting the SFP+ (enhanced Small Form-factor Pluggable):

- SFF-8084, SFP+ 1X 4 Gb/s Pluggable Transceiver Solution, Rev 1.7 September 13, 2014

- SFF-8083, SFP+ 1X 10 Gb/s Pluggable Transceiver Solution (SFP10), Rev 3.1, September 13, 2014

- SFF-8081, SFP+ 1X 16 Gb/s Pluggable Transceiver Solution (SFP16), Rev 1.4, September 13, 2014

- SFF-8402, SFP+ 1X 28 Gb/s Pluggable Transceiver Solution (SFP28), Rev 1.1, September 13, 2014

and QSFP+ (Quad Small Form-factor Pluggable):

- SFF-8685 - QSFP+ 14 Gb/s 4X Pluggable Transceiver Solution (QSFP14), Rev 0.6, June 29, 2015

- SFF-8635 - QSFP+ 4X 10 Gb/s Pluggable Transceiver Solution (QSFP10), Rev 0.6, June 29, 2015

- SFF-8665 - QSFP+ 28 Gb/s 4X Pluggable Transceiver Solution (QSFP28), Rev 1.9, June 29, 2015

building practice.

eCPRI

eCPRI Introduction

CPRI, the Industry Initiative for a Common Public Radio Interface continues to evolve: CPRI cooperation have now released the first eCPRI specification (1.0). The new specification will support the 5G Front-haul and will provide enhancements to meet the increased requirements of 5G. Following the successful program to enhance the CPRI Specification to support novel Radio Access Technologies and increasing capacity demands, Ericsson, Huawei Technologies, NEC and Nokia have released the new specification on 31 August of 2017 as previously announced, in addition to existing specifications, to encompass the developments for 5G. The new specification (eCPRI) with the 5G Front-haul support includes increased efficiency in order to meet the needs foreseen for 5G Mobile Networks. The eCPRI specification is based on new functional partitioning of the cellular base station functions, positioning the split point inside the Physical Layer (i.e. Layer 1).

The eCPRI specification offers several advantages to the base station design:

- The new interface enables ten-fold reduction of the required bandwidth.

- Required bandwidth can scale flexibly according to the user plane traffic.

- Use of packet based transport technologies will be enabled. Main stream technologies like Ethernet, open the possibility to carry eCPRI traffic and other traffic simultaneously, in the same switched network, e.g. one Ethernet network can simultaneously carry eCPRI traffic from several system vendors. In addition, the use of well-established protocols, such as Ethernet-OAM is possible for operation, administration, maintenance, provisioning, and troubleshooting of the network.

- The new interface is a real-time traffic interface enabling use of sophisticated coordination algorithms guaranteeing best possible radio performance.

- The interface is future proof allowing new feature introductions by SW updates in the radio network.

In addition to the new eCPRI specification, the work continues to further develop the existing CPRI specifications to keep it as a competitive option for all deployments with dedicated fiber connections in Fronthaul including 5G.

CPRI specifications will be openly available for the benefit of the wireless industry. Key benefits for Network Operators are the availability of a wider radio base station portfolio with adaptability to all deployment scenarios and a shorter time to market. The CPRI specifications enable base station manufacturers and component vendors to focus their research and development efforts on their core competencies.

The CPRI Initiative complements current activities in existing standardization bodies. The interfaces developed will be used for radio base station products in mobile systems.

eCPRI Releases

The following table shows eCPRI releases:

| Rel | Release_Date | Supported Specs |

|---|---|---|

| v1.0 | 2017-08-31 | the new CPRI Specification for 5G |

| v1.1 | 2018-01-31 | the new CPRI Specification for 5G |

| v1.2 | 2018-06-25 | the new CPRI Specification for 5G |

| v2.0 | 2019-05-10 | the new CPRI Specification for 5G |

Also refer to eCPRI Presentation and Requirements for the eCPRI Transport Network D0.1.

SFP

According to SFP on wikipedia:

The Small Form-factor Pluggable (SFP) is a compact, hot-pluggable optical module transceiver used for both telecommunication and data communications applications. The form factor and electrical interface are specified by a multi-source agreement (MSA) under the auspices of the Small Form Factor Committee (SFF). It is a popular industry format jointly developed and supported by many network component vendors.

An SFP interface on networking hardware provides the device with a modular interface that the user can easily adapt to various fiber optic and copper networking standards. SFP transceivers exist supporting SONET, gigabit Ethernet, Fibre Channel, and other communications standards. Due to its smaller size, the SFP has replaced the gigabit interface converter (GBIC) in most applications; the SFP is sometimes referred to as a Mini-GBIC. In fact, no device with this name has ever been officially defined in the MSAs.

SFP Standardization

The SFP transceiver is not standardized by any official standards body, but rather is specified by a multi-source agreement (MSA) among competing manufacturers. The SFP was designed after the GBIC interface, and allows greater port density (number of transceivers per cm along the edge of a mother board) than the GBIC, which is why SFP is also known as mini-GBIC. The related Small Form Factor transceiver is similar in size to the SFP, but is soldered to the host board as a through-hole device, rather than plugged into an edge-card socket.

However, as a practical matter, some networking equipment manufacturers engage in vendor lock-in practices whereby they deliberately break compatibility with “generic” SFPs by adding a check in the device’s firmware that will enable only the vendor’s own modules. Third-party SFP manufacturers have introduced SFPs with “blank” programmable EEPROMs which may be reprogrammed to match any vendor ID.

SFP Transceiver Module

Fiber Optic Cable

SFP connects to Fiber Optic Cable